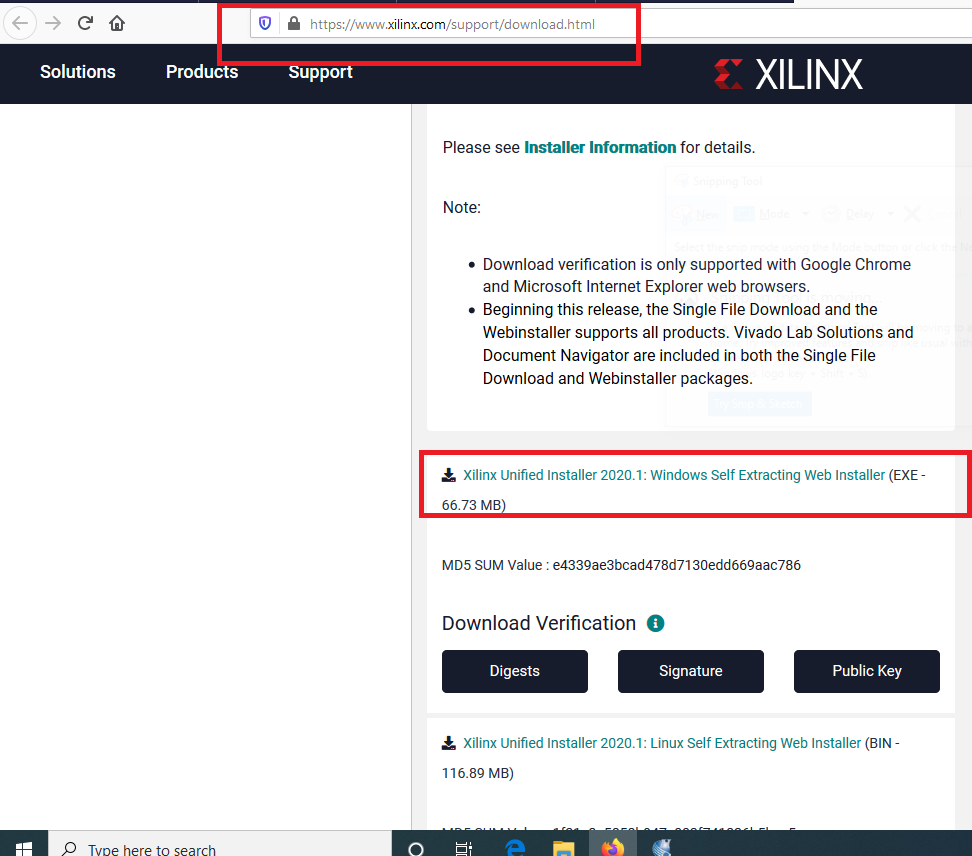

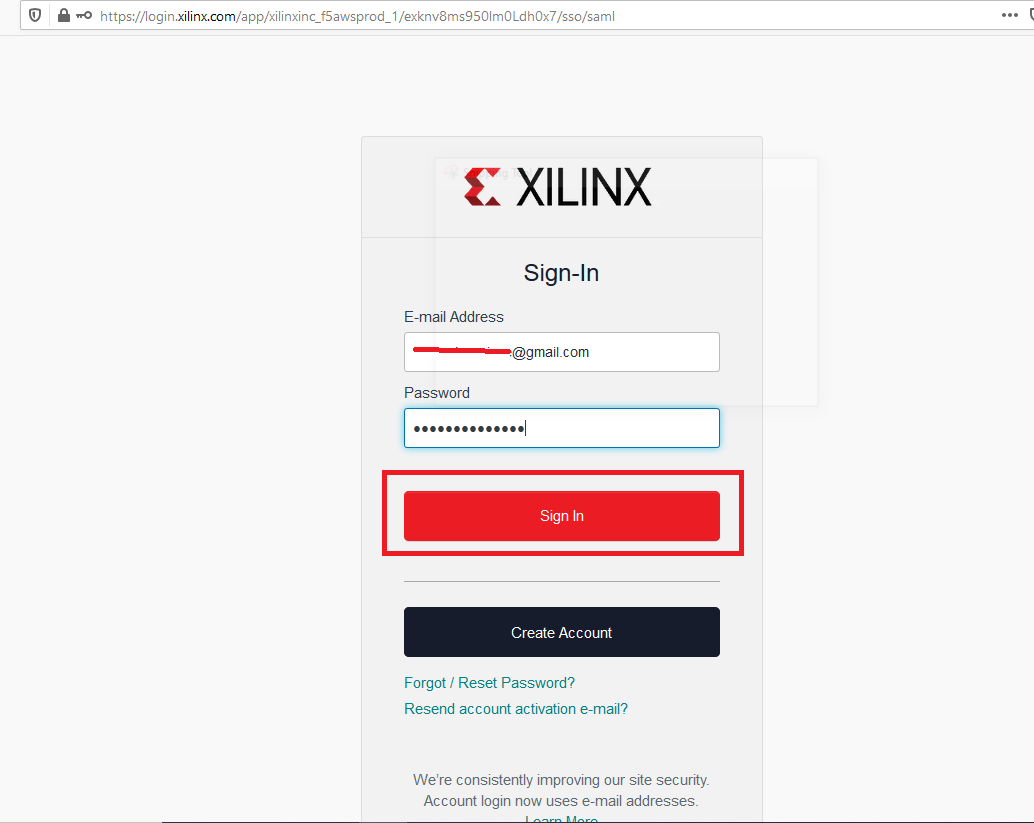

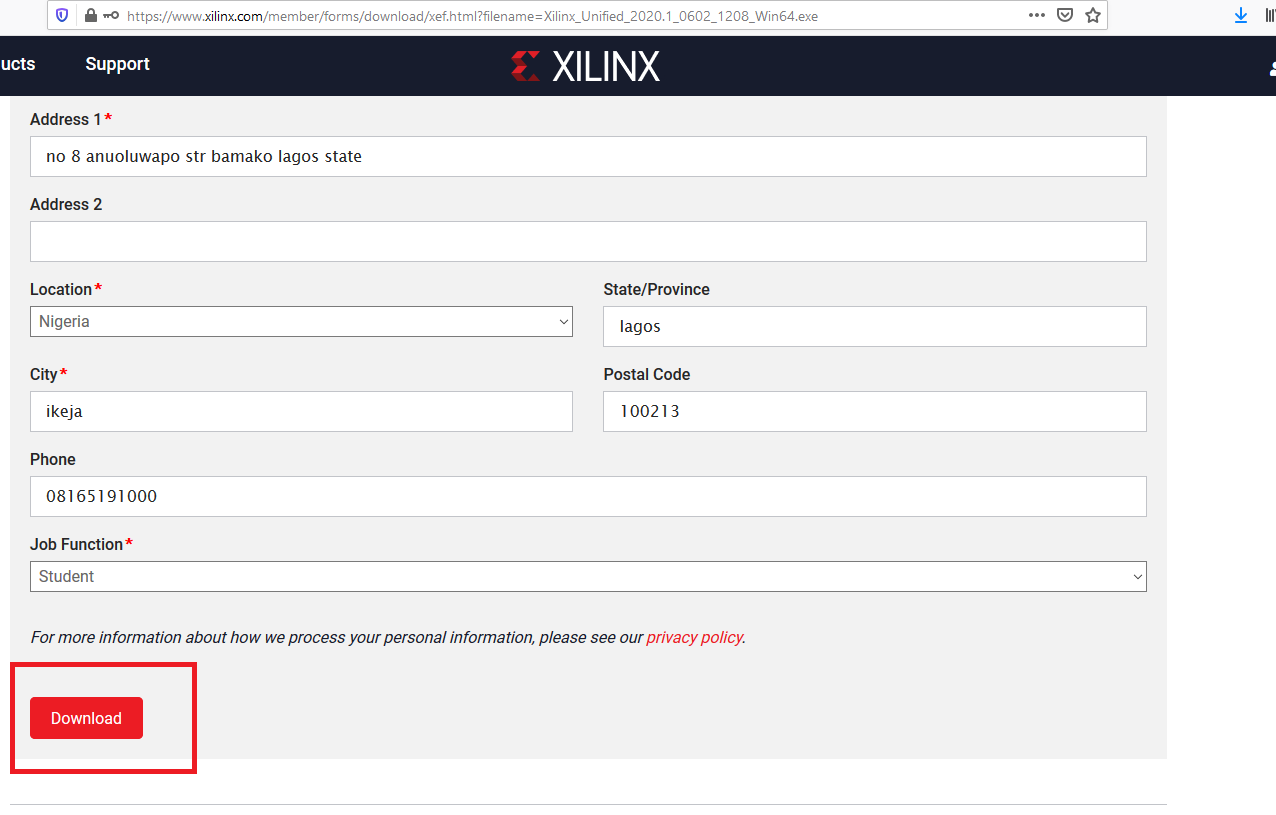

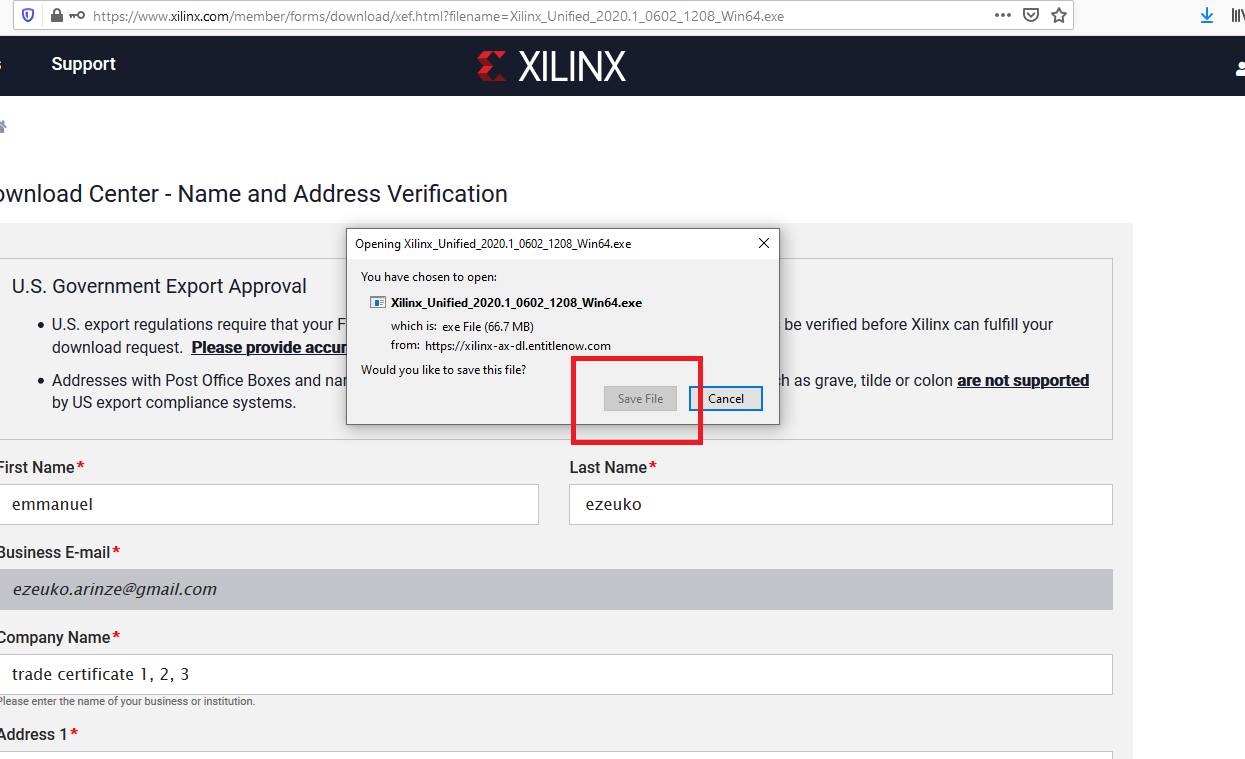

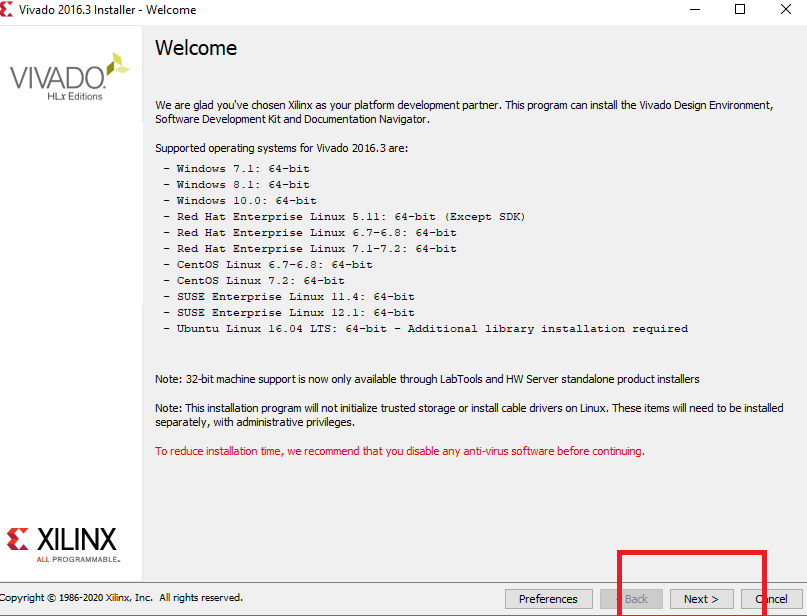

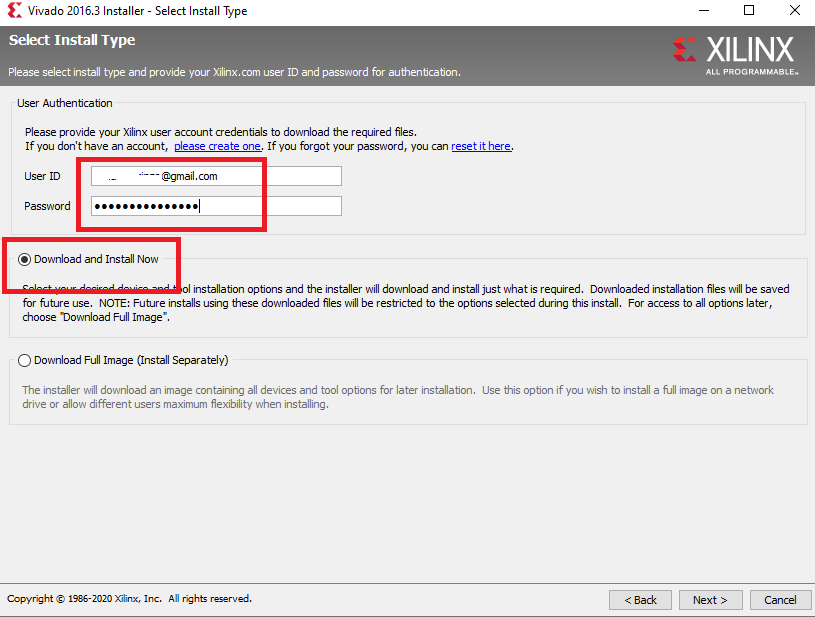

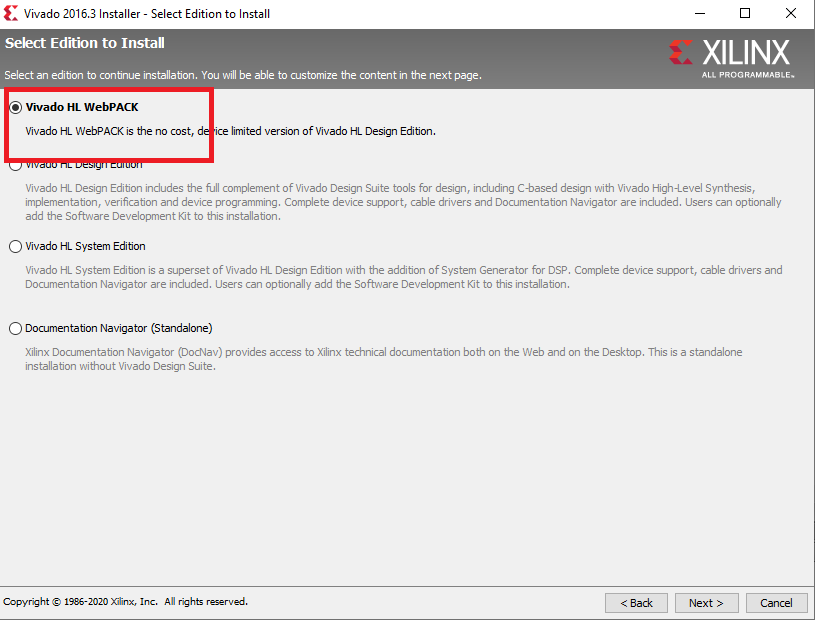

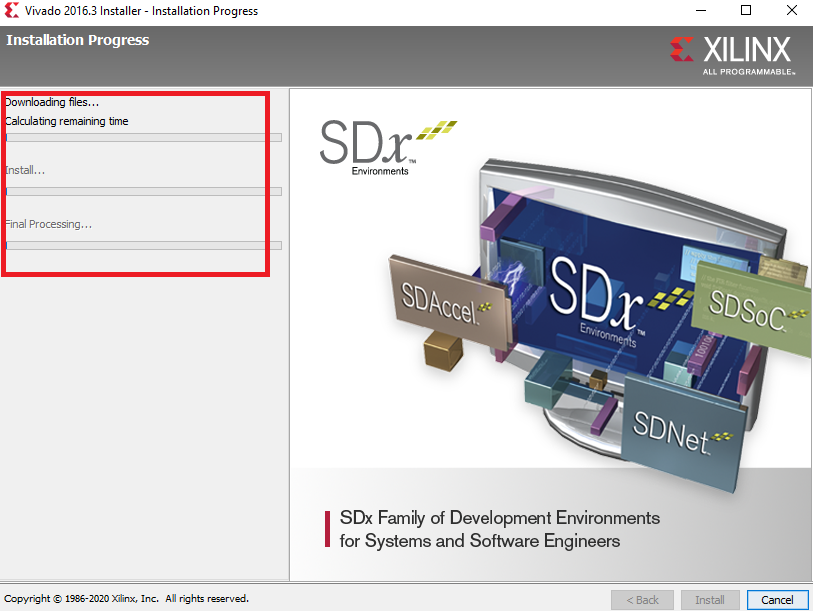

In the previous tutorial we learnt how to download, install and test our first program using the Quartus II web edition from Intels, in this tutorial we are going to download and install the Vivado design suite from Xillinx..

1. In built processors - If your application needs an inbuilt processor, then Xilinx offers one or more PowerPC cores whereas Altera offers Arm. This can often be significant because of existing codebase. Each of them also has their own version of micro controller that is available as a softcore.

2. Tool chain - it used to be that altera's software tools were more UI based and Xilinx's more script based. Earlier Xilinx enjoyed more adoption in ASIC emulation space, as such a tool flow that was more ASIC like. I haven't had recent experience with Xilinx tools but when I went to Altera Quartus from Xilinx's ISE, it was a refreshing experience.

3. Documentation - Xilinx used to be much better. Not sure how it is today. Maybe someone can comment. As for Altera, definitely needs a lot of work.

4. Do not commit the board before floor planning and place and routing especially if you are using high-speed ios - again, the recent experience with Altera has been close too nightmarish. Not sure about Xilinx. Things like not enough peripheral routing resources will prevent you from utilizing serdes blocks, lvds ios, xcvrs, etc. so what appears to be so abundant in the docs is not quite so.

5. In my last 3.125 and 10gb interfaces both midrange and high end Altera devices worked with very little tuning required. Athe parts have been running quite reliably.

6. Altera's Quartus supports SystemVerilog. Also if you use SV assertions, the tool will ignore those. The latest version has a nice tool that auto partitions the design for you. This helped to partition my designs such that I could start to use the incremental compile flow. Before the tool always tripped up. Additionally it also works with the SV interfaces. Any one can weigh in with their experience of Xilinx tools?