Processors and FPGAs (field-programmable gate arrays) are the hardworking cores of most embedded systems. Integrating the high-level management functionality of processors and the stringent, real-time operations, extreme data processing, or interface functions of an FPGA (Field Programmable Gate Array) into a single device forms an even more powerful embedded computing platform.

A system on a chip is an integrated circuit (also known as a "chip") that integrates all or most components of a computer or other electronic system. These components almost always include a central processing unit (CPU), memory, input/output ports and secondary storage, often alongside other components such as radio modems and a graphics processing unit (GPU) – all on a single substrate or microchip.[1] It may contain digital, analog, mixed-signal, and often radio frequency signal processing functions (otherwise it is considered only an application processor).

In general, there are four distinguishable types of SoCs: • SoCs built around a microcontroller, • SoCs built around a microprocessor, often found in mobile phones; • Specialized application-specific integrated circuit SoCs designed for specific applications that do not fit into the above two categories, and • Programmable SoCs (PSoC), where most functionality is fixed but some functionality is reprogrammable in a manner analogous to a field-programmable gate array.

Difference between system on Chip and MCU

System on Chip (SoC) in the term has a lot of definitions and also that will change over time but micro-controller unit (MCU) has a clear definition from decades. If we will see many documentation use these two terms inter changeably where as many also do not consider it as a correct way of using the two terms inter changeably. They both come in the area of embedded system but still with a lot similarities there is minimal differences between them which makes them distinct from each other.

The distinction between an System on Chip and a micro-controller may be little bit confusing but not that much confusing. So lets start understanding the concept clearly by knowing the difference between both.

1. Micro-controller unit (MCU) :

Micro-controller is a small computer on a single Integrated Circuit (IC) which contains a processor core, memory, and programmable input/output (I/O) peripherals, Timers and Counters and so on. It provides only minimal memory, interfaces, processing power etc.

The peripherals included on the micro-controller are lot less specific than the System on Chip. It is focused on small embedded control systems or control applications. It is sometimes abbreviated as µC, uC or MCU.

SoC is a less well defined term.It is a single chip which does everything that used to take up multiple chips. A SoC is an encapsulation of one or more of CPUs, micro-controllers, DSPs, other accelerators or supporting hardware and also more specifically it does not have a specific standard about what type of circuitry it should contain. It is intended for applications with more requirements and more complex. There might be a number of micro-controllers in a SoC.

It is more like a complete computer system on a single chip which capable to perform complex tasks which have higher resource requirement. It is sometimes abbreviated as SoC or SOC.

Difference between MCU and SoC :

| S/No | MCU | SOC |

|---|---|---|

| 01. | MCU contains single chip with less specific peripherals. | SoC contains single chip with more specific peripherals. |

| 02. | It is the encapsulation of less and limited peripheral. | It is the encapsulation of more number of peripherals. |

| 03. | It is intended for small control applications with less complexity. | It is intended for applications with more requirements and more complexity. |

| 04. | Micro-controllers cost is less than the cost of System on Chip. | System on Chip cost is more than the cost of Micro-controllers. |

| 05. | No Operating System (OS) in MCU. | SOCs can be MPU or MCU based. A compact OS is more likely if there is an OS. |

| 06. | Its power consumption is low. | Its power consumption depends on applications. |

| 07. | It provides value by minimizing cost. | It provides value by maximizing functionality. |

| 08. | MCU memory is often in KB or less and sometimes low MB. | SoC memory is often varies from MB to GB. |

| 09. | Its typical external storage varies from KB to MB and those are Flash, EEPROM. | Its typical external storage varies from MB to TB and those are Flash, SSD, HDD. |

| 10. | Its computing width are 4-bit, 8-bit, 16-bit, 32-bit. | Its computing width are 16-bit, 32-bit, 64-bit. |

| 11. | Its application example includes programmable thermostat, household appliances etc | Its application example includes smartphones and other specific applications. |

| 12. | Its product examples include Microchip technology PIC, 8051, Atmel MCUs. | Its product examples include Cypress PSoC, Qualcomm Snapdragon. |

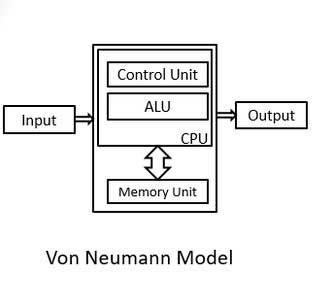

When discussing how memory is accessed at the CPU level, there are two designs to consider. The first is a Von Neumann architecture, and the second is a Harvard architecture. The major difference between the two architectures is that in a Von Neumann architecture all memory is capable of storing all program elements, data and instructions; in a Harvard architecture the memory is divided into two memories, one for data and one for instructions.

For this monograph, the major issue involved in deciding which architecture to use is that some operations have to access memory both to fetch the instruction to execute, and to access data to operate on. Because memory can only be accessed once per clock cycle, in principal a Von Neumann architecture requires at least two clock cycles to execute an instruction, whereas a Harvard architecture can execute instructions in a single cycle.

The ability in a Harvard architecture to execute an instruction in a single instruction leads to a much simpler and cleaner design for a CPU than one implemented using a Von Neumann architecture. For this first monograph a Harvard implementation will be implemented. Later monographs will look at the implementation of the CPU using the Von Neumann architecture.

Difference between Von Neumann and Harvard Architecture

| Description | Harvard Architecture | Von Neumann Architecture |

|---|---|---|

| Arrangement | In Harvard architecture, the CPU is connected with both the data memory (RAM) and program memory (ROM), separately. | In Von-Neumann architecture, there is no separate data and program memory. Instead, a single memory connection is given to the CPU |

| Hardware requirements | It requires more hardware since it will be requiring separate data and address bus for each memory. | In contrast to the Harvard architecture, this requires less hardware since only a common memory needs to be reached. |

| Space requirements | This requires more space. | Von-Neumann Architecture requires less space. |

| Speed of execution | Speed of execution is faster because the processor fetches data and instructions simultaneously . | Speed of execution is slower since it cannot fetch the data and instructions at the same time. |

| Space usage | It results in wastage of space since if the space is left in the data memory then the instructions memory cannot use the space of the data memory and vice-versa. | Space is not wasted because the space of the data memory can be utilized by the instructions memory and vice-versa. |

| Controlling | Controlling becomes complex since data and instructions are to be fetched simultaneously. | Controlling becomes simpler since either data or instructions are to be fetched at a time. |

|

|

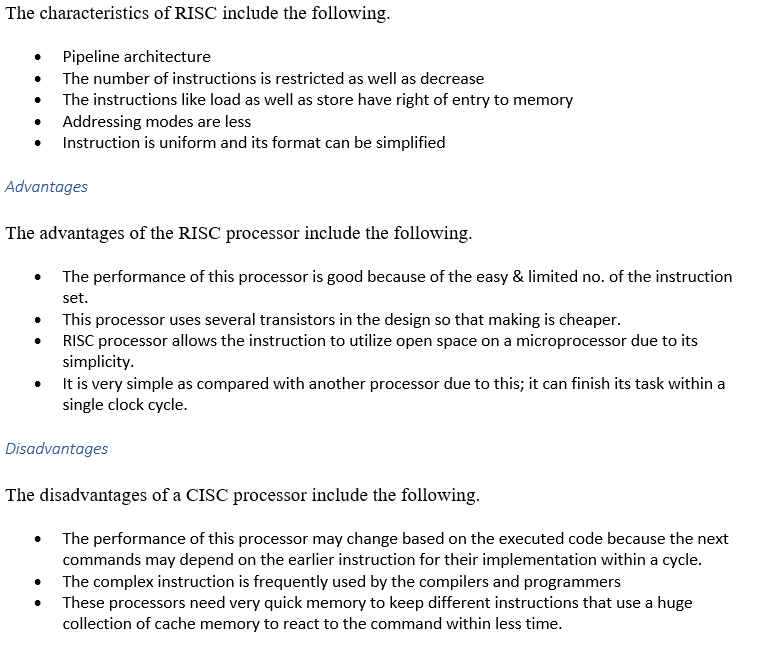

Computer ( RISC and CISC )Architecture The architecture of the Central Processing Unit (CPU) operates the capacity to function from “Instruction Set Architecture” to where it was designed. The architectural design of the CPU is Reduced instruction set computing (RISC) and Complex instruction set computing (CISC). A processor like CISC has the capacity to perform multi-step operations or addressing modes within one instruction set. It is the CPU design where one instruction works several low-level acts. For instance, memory storage, loading from memory, and an arithmetic operation. Reduced instruction set computing is a Central Processing Unit design strategy based on the vision that a basic instruction set gives great performance when combined with a microprocessor architecture that has the capacity to perform the instructions by using some microprocessor cycles per instruction.

RISC

The term RISC stands for ‘’Reduced Instruction Set Computer’’. It is a CPU design plan based on simple orders and acts fast. It iis a computer that only uses simple commands that can be divided into several instructions that achieve low-level operation within a single CLK cycle.

The RISC is a Reduced Instruction Set Computer microprocessor and its architecture includes a set of instructions that are highly customized. The main function of this is to reduce the time of instruction execution by limiting as well as optimizing the number of commands. So each command cycle uses a single clock cycle where every clock cycle includes three parameters namely fetch, decode & execute.

The kind of processor is mainly used to execute several difficult commands by merging them into simpler ones. RISC processor needs a number of transistors to design and it reduces the instruction time for execution. The best examples of RISC processors include PowerPC, SUN’s SPARC, RISC-V, Microchip PIC processors, etc.

CISC

The term CISC stands for ‘’Complex Instruction Set Computer’’. It is a CPU design plan based on single commands, which are skilled in executing multi-step operations. It was developed by the Intel Corporation and it is Complex Instruction Set Computer. This processor includes a huge collection of simple to complex instructions. These instructions are specified in the level of assembly language level and the execution of these instructions takes more time.

A complex instruction set computer is a computer where single instructions can perform numerous low-level operations like a load from memory, an arithmetic operation, and a memory store or are accomplished by multi-step processes or addressing modes in single instructions, as its name proposes “Complex Instruction Set ”.

So, this processor moves to decrease the number of instructions on every program & ignore the number of cycles for each instruction. It highlights to assemble complex instructions openly within the hardware as the hardware is always as compared with software. However, CISC chips are relatively slower as compared to RISC chips but utilize small instruction as compare with RISC. The best examples of the CISC processor include AMD, VAX, System/360 & Intel x86.